BIST-based codec IP testing

With the development of semiconductor technology, system-on-chip SOC has become a mainstream technology today. The SOC design based on IP multiplexing integrates the IP core into a system through user-defined logic (UDL) and wiring, which improves the design efficiency, speeds up the design process, and shortens the time to market. However, with the increase in design scale, the increase in integration density, the increase in IP pins, and the increase in the depth of IP implantation will inevitably make the test verification work heavy. According to statistics, in the SOC design, the test and verification work of various cores takes 60% to 80% of the entire design process. The test and verification of SOC and IP cores has become a bottleneck in the development of SOC technology. How to pass IP core verification and test efficiently and quickly in the shortest time. And integrating it into SOC has become the focus of the industry and the direction of research field urgently waiting for breakthrough and realization.

Based on the IP core multiplexing SOC, the types and sources of IP cores are different. Even if the verified IP cores are integrated, they cannot be guaranteed to be error-free. After the IP core is integrated into the SOC, its input and output ports are also embedded in the SOC. The originally measurable ports lose their original controllability and observability and become untestable.

Therefore, people have been seeking effective test verification technology. This paper presents the built-in self-test method (BIST). While designing the IP core of the codec, the design of the test shell is considered to improve the testability of the IP core.

2 test structure

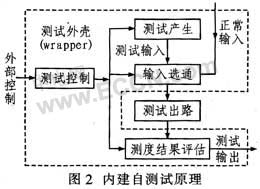

The so-called test is to apply a corresponding excitation signal to the input pin of the circuit under test, then detect the response of the output pin, and compare the response of the detected output pin with the expected pin response to determine whether the circuit is faulty process.

The purpose of the IP core test is to detect whether there are functional and timing errors in the IP core, thereby modifying the IP core and improving the reliability of the product. Generally, access, isolation, and control are used to stimulate the input end of the IP core to obtain a response and compare it with the expected response. The test structure of the embedded IP core is shown in Figure 1.

|

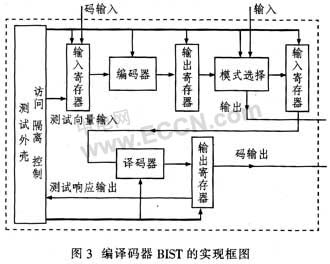

3 Built-in self-test principle

Built-in self-testing is an important method of testability design. The basic idea is to let the circuit generate test vectors instead of applying test vectors externally, and rely on itself to determine whether the results obtained are correct. The built-in self-test principle diagram is shown in Figure 2.

|

4 Implementation of built-in self-test

Controllability refers to the difficulty of driving a node to a logic state of 0 or 1. Observability refers to the difficulty of observing internal node failures from external ports; testability refers to the controllability and controllability of all nodes in the entire circuit Observability. Obviously, high testability is easier to generate test vectors and the test results are good.

In order to improve the testability of the IP core, the design of a specific circuit is considered in the design of the IP core to facilitate testing. The implementation of IP core testing with BIST generally has the following advantages: simplified test interface; improved test quality; reduced test cost; improved test reliability.

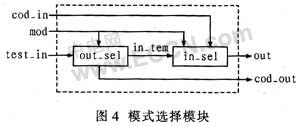

The block diagram of the IP core test implementation of the BIST-based codec is shown in Figure 3.

|

(1) In the normal state, the original code is input into the encoder, and the output code enters the decoder and is converted into the original code;

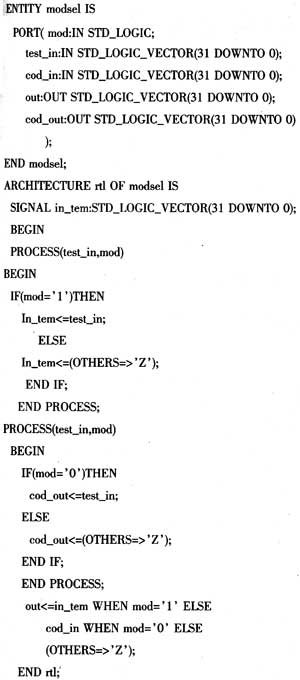

(2) In the test state, the test vector of the test shell is input to the encoder, and the code output by it directly enters the decoder. The code output by the decoder is the test response output, which is compared with the expected value; The logical structure of the module is shown in Figure 4.

|

This mode selection module realizes the switching between states, and the circuit is simple and easy to implement.

5 Conclusion

BIST provides a solvable solution for the testing of embedded cores. Its test results are obvious, fault coverage is high, and implementation is simple. By adding a test shell, access, isolation, and control of the IP core can be achieved, effectively improving the testability of the IP core. However, the use of BIST will increase the circuit area extra cost, and a trade-off must be made between the testability and the area of ​​the IP core.

Traffic Facilities,Waterproof Traffic Facilities,Outdoor Traffic Facilities,Traffic Control Devices

Yangzhou Heli Photoelectric Co., Ltd. , https://www.heli-eee.com